# **SecureSMX**<sup>TM</sup>

# **User's Guide**

Version 5.4.0

**July 2025**

by Ralph Moore and David Moore

## © Copyright 2016-2025

Micro Digital Associates, Inc. (714) 437-7333 support@smxrtos.com www.smxrtos.com

All rights reserved.

smx is a registered trademark and SecureSMX is a trademark of Micro Digital, Inc.

SecureSMX is protected by patents listed at <a href="https://www.smxrtos.com/patents.htm">www.smxrtos.com/patents.htm</a> and patents pending.

# **Table of Contents**

| PREFACE                                  | I  |

|------------------------------------------|----|

| CHAPTER 1 INTRODUCTION                   | 3  |

| 1.1 How to Use This Manual               | 3  |

| 1.2 Partitioning                         |    |

| 1.3 Advantages of Isolated Partitions    | 5  |

| 1.4 Hardware                             |    |

| 1.5 Methodology                          | 6  |

| 1.6 Security                             |    |

| 1.6.1 The Increasing Need for Security   | 6  |

| 1.6.2 Protection Goals                   |    |

| 1.6.3 What You Need                      |    |

| 1.7 SecureSMX Snapshot                   |    |

| 1.8 SecureSMX Licensing                  | 8  |

| CHAPTER 2 BACKGROUND                     | 9  |

| 2.1 MMUs vs. MPUs                        | 9  |

| 2.2 Cortex Micro Controller Units (MCUs) | 10 |

| 2.2.1 Cortex-M                           | 10 |

| 2.2.2 Cortex-M ARMM7                     | 11 |

| 2.2.3 Cortex-M ARMM8                     | 12 |

| CHAPTER 3 GETTING STARTED                | 13 |

| 3.1 Legacy Code                          | 13 |

| 3.2 New Code                             | 14 |

| 3.3 References                           | 14 |

| CHAPTER 4 BASIC THEORY                   | 17 |

| 4.1 Partitions and Tasks                 | 17 |

| 4.1.1 What are Partitions?               | 17 |

| 4.1.2 Secure Boot                        |    |

| 4.1.3 RTOS & System Services             |    |

| 4.1.4 The Vault4.1.5 Mission Critical    |    |

| 4.1.6 utasks                             |    |

| 4.1.7 ptasks                             |    |

| 4.1.8 Parent and Child Tasks             |    |

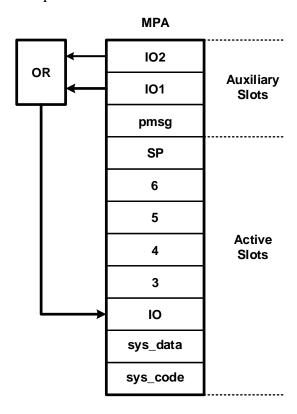

| 4.2 MPU Control                          |    |

| 4.2.1 Memory Protection Arrays and Tasks | 22 |

| 4.2.2 MPU / MPA Relationship             |    |

| 4.2.3 Active Slots                       | 24 |

| 4.2.4 Static Slots                                | 25 |

|---------------------------------------------------|----|

| 4.2.5 Auxiliary Slots                             |    |

| 4.2.6 MPU Slot Numbers & Region Overlaps          |    |

| 4.2.7 Task Stack Slot                             | 27 |

| 4.3 MPA Templates                                 | 27 |

| 4.3.1 Creating and Loading MPAs                   | 27 |

| 4.3.2 Using Parent and Child Tasks                |    |

| 4.3.3 Using ARMM7 MPU Subregions                  |    |

| 4.3.4 Creating ARMM7 MPA Templates                | 32 |

| 4.3.5 Creating ARMM8 MPA Templates                |    |

| 4.3.6 Fast MPU Load                               |    |

| 4.3.7 Template Errors                             |    |

| 4.3.8 Standard Regions                            | 35 |

| 4.4 Linker Command File                           | 35 |

| 4.4.1 First Sections                              | 36 |

| 4.4.2 Region Block Definitions                    |    |

| 4.4.3 Block Ordering                              |    |

| 4.5 Defining Sections                             |    |

| 4.5.1 Section Prefixes                            |    |

| 4.5.2 Command Line Switches                       |    |

| 4.5.3 Section Pragmas                             |    |

| 4.5.4 Template Macros                             |    |

| 4.5.5 String Literals                             |    |

| 4.6 Map Files                                     |    |

| 4.6.1 ARMM7                                       |    |

| 4.6.2 ARMM8                                       |    |

| 4.6.3 MpuMapper                                   |    |

|                                                   |    |

| 4.7 Regions                                       |    |

| 4.7.1 Insufficient MPU Slots                      |    |

| 4.7.2 Combined Regions                            |    |

| 4.7.3 Common Regions                              |    |

| 4.7.4 I/O Regions                                 |    |

| 4.7.5 I/O Regions Using Subregions                |    |

| 4.8 Interrupts and Exceptions                     | 50 |

| 4.8.1 Priorities                                  |    |

| 4.8.2 Enabling ISRs and Exception Handlers to Run |    |

| 4.8.3 Interrupts                                  |    |

| 4.8.4 Writing ISRs                                |    |

| 4.8.5 Exceptions                                  |    |

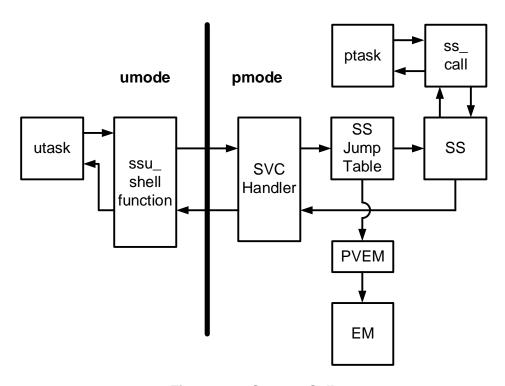

| 4.9 SVC API                                       | 54 |

| 4.9.1 SVC Calls                                   | 54 |

| 4.9.2 SVC Call Mechanism                          | 56 |

| 4.9.3 Restricted Services                         |    |

| 4.9.4 Custom SSTs                                 |    |

| 4.9.5 Partially Restricted Services               |    |

| 4.9.6 Mixed Code Modules                          | 60 |

| 4.10 Processor Control                            | 61 |

| 4.10.1 smx Task Switching                         | 61 |

|                                                   |    |

| 4.10.2 From pmode to umode                               | 62       |

|----------------------------------------------------------|----------|

| 4.10.3 Memory Protection Arrays, MPAs                    |          |

| 4.10.4 What Good are ptasks?                             |          |

| 4.10.5 Hacking a ptask                                   |          |

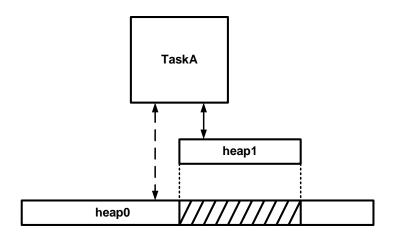

| 4.11 Dynamic Features                                    | 66       |

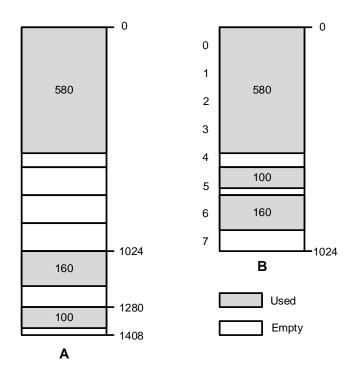

| 4.11.1 eheap and smx_Heap                                | 66       |

| 4.11.2 The Need for Multiple Heaps                       | 67       |

| 4.11.3 Allocating Heap Space                             | 67       |

| 4.11.4 Creating a Heap                                   | 68       |

| 4.11.5 Heap Manager                                      | 69       |

| 4.11.6 Task Stacks                                       |          |

| 4.11.7 PSPLIM and MSPLIM                                 |          |

| 4.11.8 Task Local Storage                                |          |

| 4.11.9 Dynamic Regions                                   |          |

| 4.11.10 Protected Data Blocks                            |          |

| 4.11.11 Protected Messages                               |          |

| 4.12 Miscellaneous                                       | 76       |

| 4.12.1 Standard C Library Functions                      | 76       |

| 4.12.2 Partition Isolation vs. ucom Regions              |          |

| 4.12.3 HAL Code                                          |          |

|                                                          |          |

| CHAPTER 5 PARTITION PORTALS                              | 79       |

| 5.1 Introduction                                         | 79       |

| 5.1.1 Isolated Partitions                                |          |

| 5.1.2 Function Call APIs                                 |          |

| 5.1.3 Partition Portals                                  |          |

| 5.2 Protected Messages                                   |          |

| ~                                                        |          |

| 5.2.1 pmsg Structure                                     |          |

| 5.2.2 Sending a pmsg                                     |          |

| 5.2.3 Receiving a pmsg5.2.4 Message Priority Inheritance |          |

| 5.2.5 Dual MPA Slots for ARMM8                           |          |

|                                                          |          |

| 5.3 Free Message Portal                                  |          |

| 5.3.1 Configurations                                     |          |

| 5.3.2 Portal Creation                                    |          |

| 5.3.3 Client Open                                        | 87       |

| 5.3.4 Client Operation                                   | ^^       |

| •                                                        |          |

| 5.3.7 Portal Deletion                                    | 89       |

|                                                          | 89<br>90 |

| 5.3.8 More Flexible Operation                            |          |

| 5.3.8 More Flexible Operation                            |          |

| 5.4 Tunnel Portal                                        |          |

| 5.4 Tunnel Portal                                        |          |

| 5.4.1 Get pmsg (by client)                               |          |

| 5.4 Tunnel Portal                                        |          |

| 5.5 Shell Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |

| 5.5.1 Mapping Functions to Shell Functions                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |

| 5.5.2 Creating a pmsg                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |

| 5.5.3 Portal Server Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |

| 5.6 Sending Free Messages to Tunnel Portals                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |

| 5.7 Other Portal Topics                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107                                                                 |

| 5.7.1 Portal Access Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |

| 5.7.2 Portal Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

| 5.7.3 Chained Portals                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |

| 5.7.4 Server Callbacks                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                     |

| 5.7.5 Who's The Boss?5.7.6 Client Data                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                     |

| 5.7.7 Window Portal                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |

| 5.8 Console Portal                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |

| 5.9 Middleware Portals                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                     |

| 5.9.1 smxFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |

| 5.9.2 smxNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |

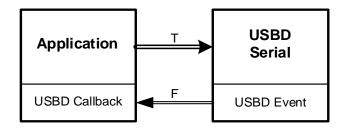

| 5.9.3 smxUSBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |

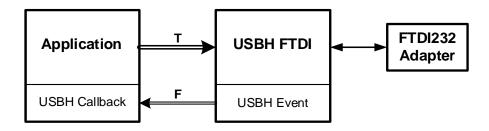

| 5.9.4 smxUSBH                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |

| 5.10 Portal Tips                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11/                                                                 |

| APTER 6 ADVANCED THEORY                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 119                                                                 |

| 6.1 System Services                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110                                                                 |

| 6.1 System Services                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

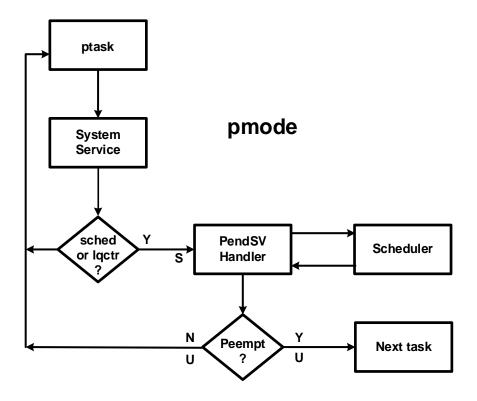

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 120                                                                 |

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 120                                                                 |

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |

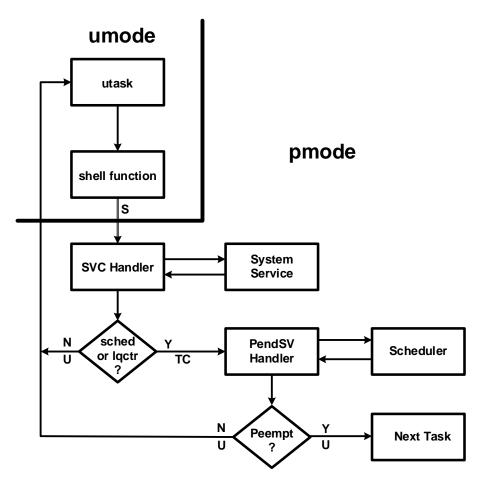

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 120<br>121<br>123<br>123<br>126<br>126<br>126<br>126                |

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 126 127 128 129 129 129 129 129 129 129 129 127 127                 |

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 126 127 128 129 129 129 129 129 129 129 127 129                     |

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 126 127 128 129 129 129 129 129 129 129 127 129                     |

| 6.1.1 System Calls from pmode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 120 121 123 123 125 126 126 126 127 127 127 127 128 130             |

| 6.1.1 System Calls from pmode 6.1.2 System Calls from umode 6.2 Critical Sections 6.2.1 SecureSMX Object Priorities. 6.2.2 Interrupt Disabling and Masking in Tasks 6.2.3 Other Methods to Protect Critical Sections 6.3 Cache Control 6.4 Porting SecureSMX 6.4.1 To Another Toolchain. 6.4.2 To Another RTOS. 6.4.3 To Another Processor 6.5 Runtime Limiting 6.5.1 Guidelines 6.5.2 Approach. 6.5.3 Enabling Runtime Limiting. 6.5.4 Adaptive Time slicing.                    | 120 121 123 123 125 126 126 126 127 127 127 127 127 129 130 131     |

| 6.1.1 System Calls from pmode 6.1.2 System Calls from umode 6.2 Critical Sections 6.2.1 SecureSMX Object Priorities. 6.2.2 Interrupt Disabling and Masking in Tasks 6.2.3 Other Methods to Protect Critical Sections 6.3 Cache Control 6.4 Porting SecureSMX 6.4.1 To Another Toolchain. 6.4.2 To Another RTOS. 6.4.3 To Another Processor 6.5 Runtime Limiting 6.5.1 Guidelines. 6.5.2 Approach. 6.5.3 Enabling Runtime Limiting. 6.5.4 Adaptive Time slicing.                   | 120 121 123 123 125 126 126 127 127 127 127 127 127 128 130 131     |

| 6.1.1 System Calls from pmode 6.1.2 System Calls from umode 6.2 Critical Sections 6.2.1 SecureSMX Object Priorities 6.2.2 Interrupt Disabling and Masking in Tasks 6.2.3 Other Methods to Protect Critical Sections 6.3 Cache Control 6.4 Porting SecureSMX 6.4.1 To Another Toolchain 6.4.2 To Another RTOS 6.4.3 To Another Processor 6.5 Runtime Limiting 6.5.1 Guidelines 6.5.2 Approach 6.5.3 Enabling Runtime Limiting 6.5.4 Adaptive Time slicing 6.6 Tokens 6.6.1 General | 120 121 123 123 123 125 126 126 127 127 127 127 127 127 129 130 131 |

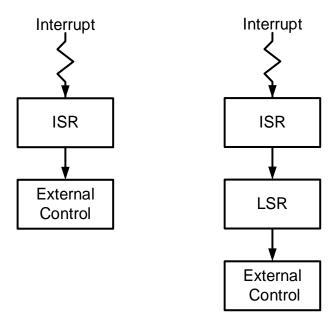

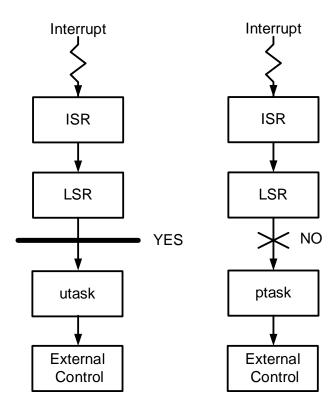

| 6.7.1 The ISR Problem                         | 133 |

|-----------------------------------------------|-----|

| 6.7.2 LSR Types and Operation                 |     |

| 6.7.3 Performance                             |     |

| 6.7.4 Resulting Security                      | 135 |

| 6.8 Task Privilege Levels                     | 135 |

| 6.8.1 Description                             | 135 |

| CHAPTER 7 PARTITION DEMOS                     | 137 |

|                                               |     |

| 7.1 Getting Started                           |     |

| 7.2 Creating an Isolated Umode Partition Demo |     |

| 7.2.0 pd0                                     | 138 |

| 7.2.1 pd1                                     |     |

| 7.2.2 pd2                                     |     |

| 7.2.3 pd3                                     |     |

| 7.2.4 pd4                                     |     |

| 7.2.5 pd5                                     |     |

| 7.2.6 pd6                                     | 151 |

| CHAPTER 8 IMPLEMENTATION                      | 153 |

| 8.1 Planning                                  |     |

| 8.1.1 Security Plan                           |     |

| 8.1.2 Reliability Plan                        |     |

| 8.1.3 When to Add MPU Support                 |     |

| 8.2 Project Approach                          |     |

| 8.2.1 Legacy Code                             |     |

| 8.2.2 New Code                                |     |

| 8.2.3 Iterative Process                       |     |

| 8.2.4 Keeping a Log and Backups               |     |

| 8.3 Working Base                              |     |

| 8.3.1 Getting Started                         |     |

| 8.4 Partitions                                | 158 |

| 8.4.1 Creating Partitions                     |     |

| 8.4.2 Partition Overlap                       |     |

| 8.4.3 Using Region Tails                      |     |

| 8.4.4 Partition Updating                      |     |

| 8.5 Templates & Regions                       |     |

| 8.5.1 Creating Templates                      |     |

| 8.5.2 Code and Data Regions                   |     |

| 8.5.3 I/O Regions                             | 161 |

| 8.5.4 Too Many I/O Regions                    |     |

| 8.5.5 MPU Region Details                      | 163 |

| 8.5.6 ucom_code Region                        |     |

| 8.5.7 Using TLS to Reduce Regions             | 164 |

| 8.6 Using the Linker                          | 165 |

| 8.6.1 Block in Block                          | 165 |

| 8.6.2 Initialized Variables                   | 166 |

|    | 8.7 Tasks                                                         | 166 |

|----|-------------------------------------------------------------------|-----|

|    | 8.7.1 Creating ptasks                                             | 166 |

|    | 8.7.2 Converting from ptask to utask                              | 166 |

|    | 8.7.3 Dealing with Restricted and New Services                    |     |

|    | 8.7.4 Dealing with Shared Code and Data                           |     |

|    | 8.7.5 Permanent ptasks                                            |     |

|    | 8.7.6 Using Child Tasks to Reduce Regions                         |     |

|    | 8.8 Creating SVC Calls                                            |     |

|    | 8.9 Portals                                                       | 170 |

|    | 8.9.1 Creating a Free Message Portal                              | 170 |

|    | 8.9.2 Creating a Tunnel Portal                                    |     |

|    | 8.9.3 Tunnel Portal Client Shells and Server Cases for Most Calls |     |

|    | 8.9.4 Tunnel Portal Data Block Transfers in Item Units            |     |

|    | 8.9.5 Data Block Transfer Considerations                          |     |

|    | 8.9.6 Portal Configuration Settings                               |     |

|    | 8.10 Miscellaneous                                                |     |

|    | 8.10.1 Heap Calls                                                 |     |

|    | 8.10.2 Performance Measurements                                   |     |

|    | 8.10.3 Where Am I?                                                |     |

|    | 8.10.4 Event Buffer<br>8.10.5 Reset Vector                        |     |

|    | 8.10.6 ISRs and LSRs                                              |     |

|    | 8.10.7 Critical Sections                                          |     |

|    | 8.11 Reducing Memory Waste for ARMM7                              |     |

|    | 8.11.1 Using MpuPacker                                            |     |

|    | 8.11.2 Reducing Block Tails                                       |     |

|    | 8.11.3 Reducing Region Block Gaps                                 |     |

|    | 8.11.4 Using Plug Blocks                                          |     |

|    | 8.11.5 Reducing Region Block Sizes                                | 188 |

|    | 8.11.6 Restructuring Regions                                      |     |

|    | 8.11.7 Handling Aligned Blocks within Aligned Blocks              |     |

|    | 8.11.8 Reducing code and data sizes                               |     |

|    | 8.11.9 Conclusion                                                 |     |

|    | 8.12 Prerelease Checklist                                         |     |

|    | 8.13 Design Tips                                                  | 191 |

|    | 8.14 Measurements                                                 | 192 |

|    | 8.14.1 Size                                                       | 192 |

|    | 8.14.2 General Performance                                        |     |

|    | 8.14.3 Thumb Drive Performance                                    |     |

|    | 8.14.4 SD Card Performance                                        |     |

|    | 8.14.5 ARMM7 Memory Waste                                         |     |

|    | 8.15 EWARM Tool Issues                                            | 195 |

| CH | IAPTER 9 DEBUGGING                                                | 197 |

|    | 9.1 Using Configuration Constants                                 | 197 |

|    | 9.1.1 SMX_CFG_SSMX                                                |     |

|    | 9.1.2 SMX_CFG_SSMX_ENABLE                                         |     |

| 9.1.3 MP_MPA_DEV                                                                                                                                                                                                                                                                                           |                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                            | AL197                                                           |

|                                                                                                                                                                                                                                                                                                            |                                                                 |

|                                                                                                                                                                                                                                                                                                            |                                                                 |

|                                                                                                                                                                                                                                                                                                            |                                                                 |

|                                                                                                                                                                                                                                                                                                            |                                                                 |

|                                                                                                                                                                                                                                                                                                            |                                                                 |

| •                                                                                                                                                                                                                                                                                                          |                                                                 |

| <u> </u>                                                                                                                                                                                                                                                                                                   |                                                                 |

| 3 33                                                                                                                                                                                                                                                                                                       | indows199                                                       |

|                                                                                                                                                                                                                                                                                                            | m200                                                            |

| 9                                                                                                                                                                                                                                                                                                          | F                                                               |

|                                                                                                                                                                                                                                                                                                            |                                                                 |

|                                                                                                                                                                                                                                                                                                            | 202                                                             |

|                                                                                                                                                                                                                                                                                                            | ity Features203                                                 |

| •                                                                                                                                                                                                                                                                                                          | 203                                                             |

|                                                                                                                                                                                                                                                                                                            | 204                                                             |

|                                                                                                                                                                                                                                                                                                            | 204                                                             |

|                                                                                                                                                                                                                                                                                                            | ow204                                                           |

|                                                                                                                                                                                                                                                                                                            |                                                                 |

| •                                                                                                                                                                                                                                                                                                          | 205                                                             |

| ~ F D                                                                                                                                                                                                                                                                                                      | 205                                                             |

| •                                                                                                                                                                                                                                                                                                          | 205                                                             |

| •                                                                                                                                                                                                                                                                                                          |                                                                 |

| 9.6 Debug Tips                                                                                                                                                                                                                                                                                             |                                                                 |

| 9.6 Debug Tips<br>9.7 C-SPY Tool Issues                                                                                                                                                                                                                                                                    |                                                                 |

| 9.6 Debug Tips<br>9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESN                                                                                                                                                                                                                                             |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESN  mp_FPortalClose                                                                                                                                                                                                                               |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESN  mp_FPortalClose                                                                                                                                                                                                                               |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESN  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete                                                                                                                                                                                           |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESN  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete                                                                                                                                                                                           |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen                                                                                                                                                                           |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive                                                                                                                                                        |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend                                                                                                                                        |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_FTPortalSend                                                                                                                       |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_MPACreate                                                                                                                          | 206 208  X SERVICES 209 209 210 211 211 212 212                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_FTPortalSend  mp_MPACreate LSR                                                                                                     |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_MPACreate  mp_MPACreateLSR  mp_MPUSlotLoad                                                                                         | 206  208  X SERVICES  209  210  211  211  212  213  214  215    |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESN  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_FPortalSend  mp_MPACreate  mp_MPACreateLSR  mp_MPUSlotLoad  mp_MPASlotMove                                                         | 206 208  X SERVICES 209 209 210 211 211 212 212 213 214 215 216 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_FTPortalSend  mp_MPACreate LSR  mp_MPACreateLSR  mp_MPUSlotLoad  mp_MPASlotMove  mp_MPUSlotSwap                                    |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESN  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalSend  mp_FPortalSend  mp_MPACreate  mp_MPACreate LSR  mp_MPUSlotLoad  mp_MPASlotMove  mp_MPUSlotSwap  mp_TPortalCall                                           |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_FPortalSend  mp_MPACreate LSR  mp_MPACreateLSR  mp_MPASlotMove  mp_MPUSlotSwap  mp_TPortalCall  mp_TPortalClose                    |                                                                 |

| 9.6 Debug Tips 9.7 C-SPY Tool Issues  APPENDIX A.1 SECURESM  mp_FPortalClose  mp_FPortalCreate  mp_FPortalDelete  mp_FPortalOpen  mp_FPortalReceive  mp_FPortalSend  mp_FTPortalSend  mp_MPACreate LSR  mp_MPACreateLSR  mp_MPUSlotLoad  mp_MPUSlotSwap  mp_TPortalCall  mp_TPortalClose  mp_TPortalCreate |                                                                 |

| mp_TportalOpen                                      | 221 |

|-----------------------------------------------------|-----|

| mp_TPortalReceive                                   | 222 |

| mp_TPortalSend                                      | 223 |

| mp_TPortalServer                                    | 224 |

| mp_RegionGetHeapR                                   | 226 |

| mp_RegionGetHeapT                                   | 227 |

| mp_RegionGetPooIR                                   | 227 |

| mp_RegionGetPoolT                                   | 228 |

| mp_RegionMakeR                                      | 229 |

| mp_RegionMakeT                                      | 230 |

| APPENDIX A.2 SMX PROTECTED BLOCK & MESSAGE SERVICES | 231 |

| smx_PBlockGetHeap                                   | 231 |

| smx_PBlockGetPool                                   | 232 |

| smx_PBlockMake                                      | 233 |

| smx_PBlockRelHeap                                   | 234 |

| smx_PBlockRelPool                                   | 234 |

| smx_PMsgGetHeap                                     | 235 |

| smx_PMsgGetPool                                     | 236 |

| smx_PMsgMake                                        | 237 |

| smx_PMsgReceive                                     | 238 |

| smx_PMsgReceiveStop                                 | 239 |

| smx_PMsgRel                                         | 240 |

| smx_PMsgReply                                       | 241 |

| smx_PMsgSend                                        | 242 |

| smx_PMsgSendB                                       | 243 |

| APPENDIX B: LINKER COMMAND FILES                    | 245 |

| ARMM7                                               | 245 |

| ARMM8                                               | 248 |

| APPENDIX C: GLOSSARY                                | 253 |

| APPENDIX D: SMX API LIMITATIONS                     | 255 |

# **Table of Figures**

| FIGURE 1.1 NON-PARTITIONED SOFTWARE                                     | 4   |

|-------------------------------------------------------------------------|-----|

| FIGURE 1.2 PARTITIONED SOFTWARE                                         | 4   |

| FIGURE 2.1 MPU OPERATION                                                | 11  |

| FIGURE 4.1 PARTITIONS                                                   | 17  |

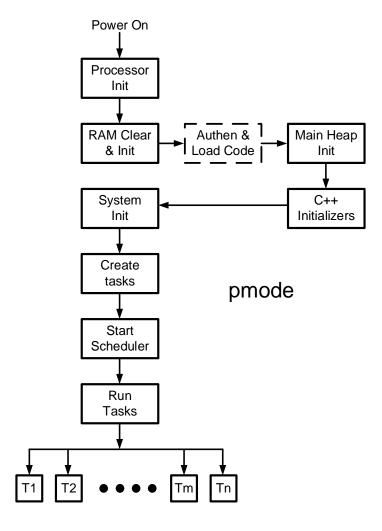

| FIGURE 4.2 SECURE BOOT AND STARTUP                                      | 19  |

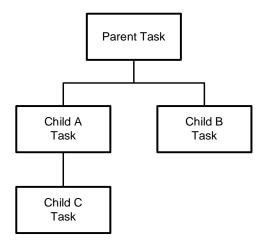

| FIGURE 4.3 PARENT AND CHILD TASKS                                       | 21  |

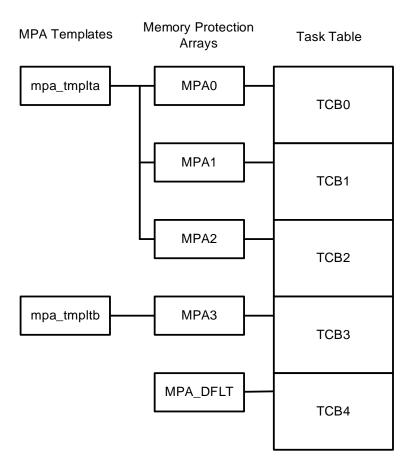

| FIGURE 4.4 MPA TEMPLATES, MEMORY PROTECTION ARRAYS, AND TASKS           | 22  |

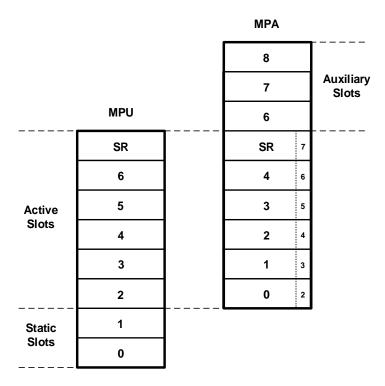

| FIGURE 4.5 MPU / MPA ALIGNMENT                                          |     |

| FIGURE 4.6 USING EXPANSION SLOTS                                        |     |

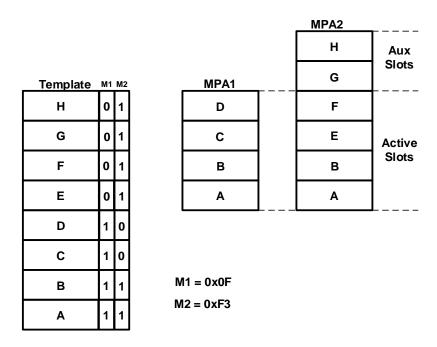

| FIGURE 4.7 TEMPLATE LOADED INTO MPAS                                    |     |

| FIGURE 4.8 USING ARMM7 SUBREGION OVERLAYS                               | 31  |

| FIGURE 4.9 REGION WITH SUBREGION 5-7 DISABLES                           | 37  |

| FIGURE 4.10 MINIMAL INTERRUPT PROCESSING                                |     |

| FIGURE 4.11 TASK INTERRUPT PROCESSING                                   | 52  |

| FIGURE 4.12 SYSTEM CALLSFIGURE 4.13 MPA FOR PTASK                       | 56  |

|                                                                         |     |

| FIGURE 4.14 MPA FOR UTASK                                               |     |

| FIGURE 4.15 DEDICATED HEAP FROM MAIN HEAP                               | 68  |

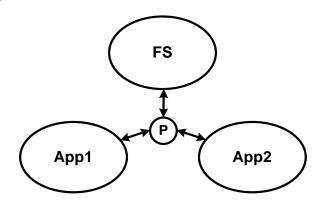

| FIGURE 5.1 DESIRED ISOLATION BETWEEN PARTITIONS                         | 79  |

| FIGURE 5.2 LOSS OF PARTITION ISOLATION                                  | 79  |

| FIGURE 5.3 PARTITION ISOLATION USING FS PORTAL P                        |     |

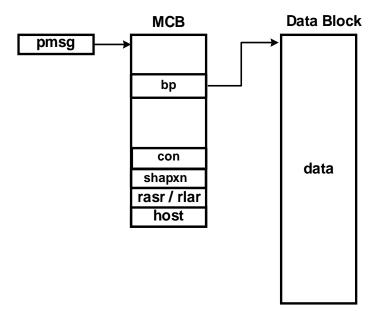

| FIGURE 5.4 PROTECTED MESSAGE STRUCTURE                                  |     |

| FIGURE 5.5 PMSG TRANSFERFIGURE 5.6 FREE MESSAGE PROTOCOL CONFIGURATIONS | 82  |

|                                                                         |     |

| FIGURE 5.7 TUNNEL PORTAL                                                | 93  |

| FIGURE 5.8 TUNNEL PORTAL OPERATION                                      |     |

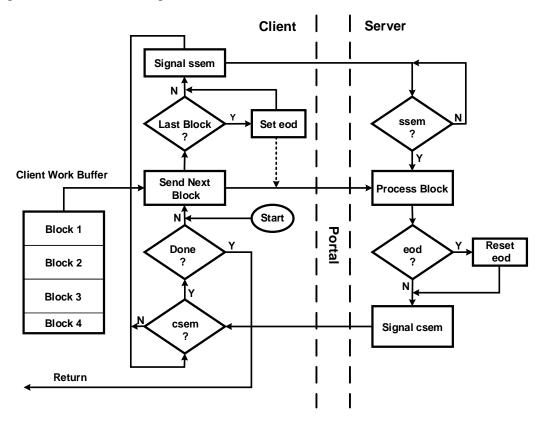

| FIGURE 5.9 MULTIBLOCK SEND                                              |     |

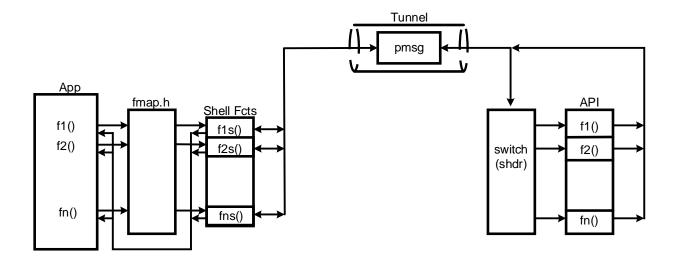

| FIGURE 5.10 SHELL FUNCTIONS                                             |     |

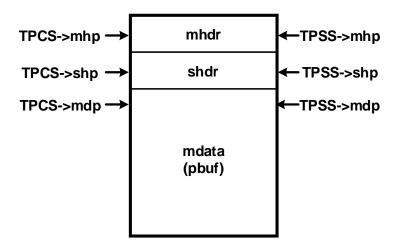

| FIGURE 5.11 PMSG FORMAT                                                 |     |

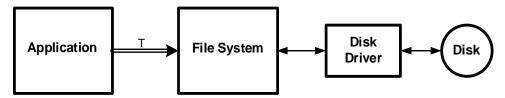

| FIGURE 5.12 SMXFS PORTAL                                                |     |

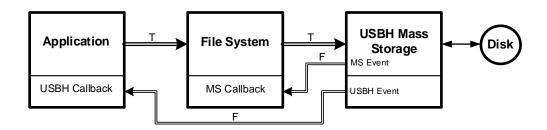

| FIGURE 5.13 SMXFS AND SMXUSBH MASS STORAGE CHAINED PORTALS              |     |

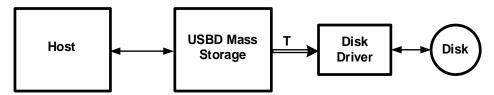

| FIGURE 5.14 SMXUSBD MASS STORAGE PORTAL                                 |     |

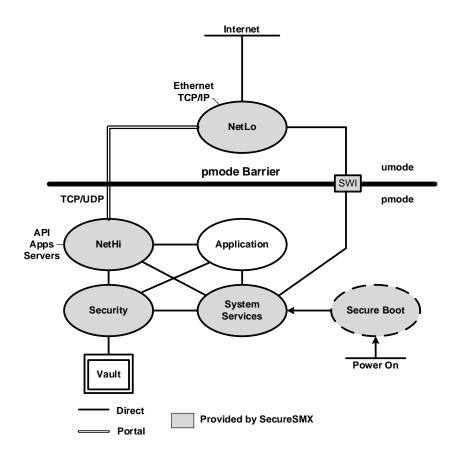

| FIGURE 5.15 SMXNS TRANSPORT LAYER (HI/LO) PORTAL                        |     |

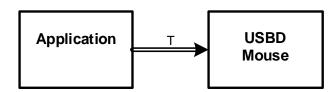

| FIGURE 5.16 SMXUSBD MOUSE PORTAL                                        |     |

| FIGURE 5.17 SMXUSBD SERIAL PORTAL                                       |     |

| FIGURE 5.18 SMXUSBH FTDI232 SERIAL PORTAL                               |     |

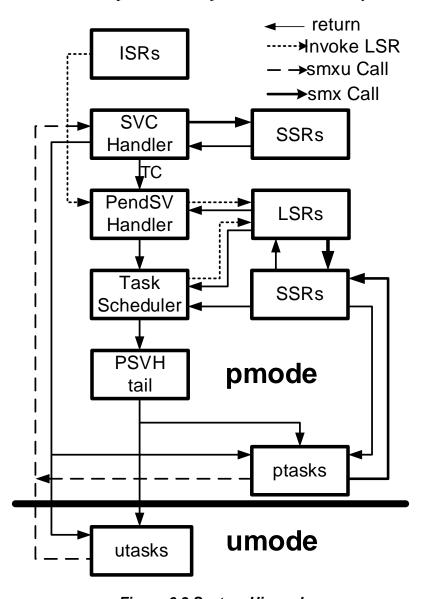

| FIGURE 6.1 SYSTEM CALL FROM PTASK                                       | 120 |

| FIGURE 6.2 SYSTEM CALL FROM UMODE                                       |     |

| FIGURE 6.3 SYSTEM HIERARCHY                                             |     |

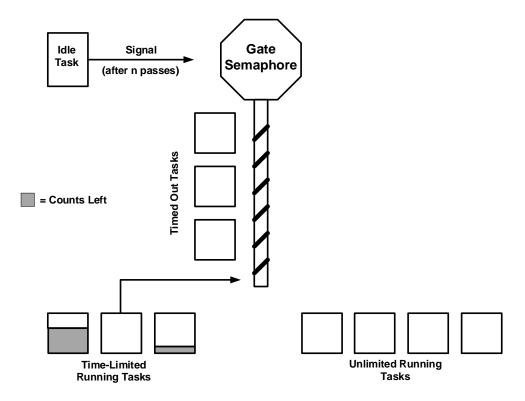

| FIGURE 6.4 RUNTIME LIMITING                                             |     |

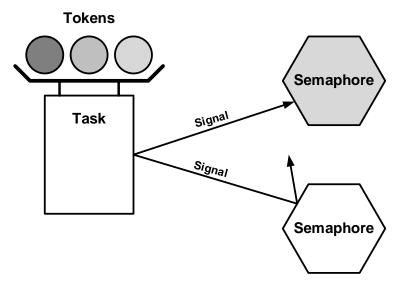

| FIGURE 6.5 TOKENS                                                       |     |

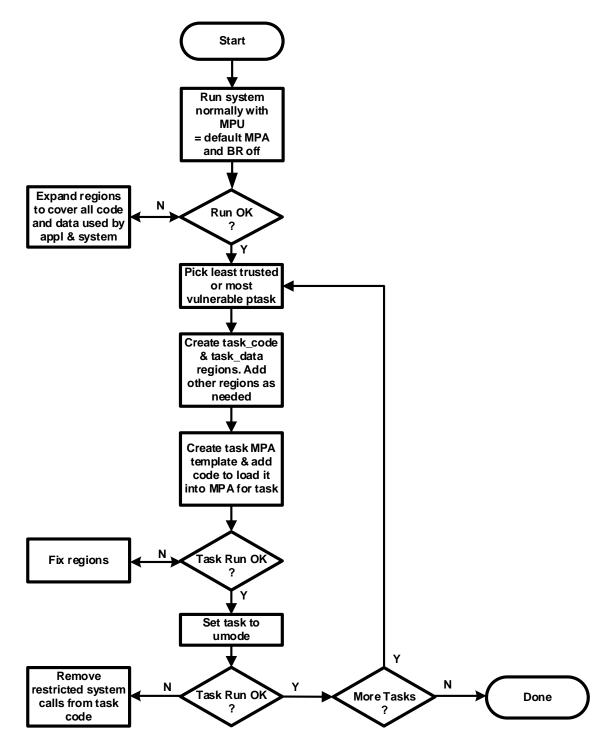

| FIGURE 8.1 CONVERTING PTASKS TO LITASKS                                 | 156 |

# **Preface**

Adding security to an embedded system increases its complexity and may increase its development time. However, adding isolated partitions with limits has some offsetting advantages such as easier system integration and easier debugging, resulting in:

- 1. Little or no increase in actual development time.

- 2. Better products.

- 3. Reduced future security problems.

SecureSMX can be viewed as a different way to develop microcontroller-based applications. It provides a methodology in which software is modularized, then modules are placed into isolated partitions, and those are moved into unprivileged mode (*umode*). Partitions are allowed to access only a restricted set of system services and tokens are required to access smx objects in order to perform kernel services. Token control is strictly within SecureSMX and cannot be compromised from umode. Communication between partitions is restricted to standardized *portals*. All limitations are hardware-enforced.

SecureSMX provides a toolbox containing many tools to deal with security problems. It is not a one-size-fits-all solution. In fact, it is specifically aimed at not requiring that trusted code be modified. Instead, it is aimed at partitioning untrusted and vulnerable software into isolated partitions and then imposing limitations so that malware in those partitions cannot harm the rest of the system. Whereas designing security in from the start is the best approach, SecureSMX also supports incremental security improvement of existing products.

SecureSMX currently supports MCUs with Memory Protection Units based upon the Cortex-M v7 and v8 architectures. These account for about 80% of all MCUs currently being produced.

# **Chapter 1 Introduction**

#### 1.1 How to Use This Manual

The next three chapters of this manual cover the theory of the SecureSMX methodology. Chapter 4 covers the features of SecureSMX. Chapter 5 presents portals, which you may not need until late in your project. Chapter 6 presents advanced theory, which you may not need at all.

We recommend reading the introductory material, scanning the theoretical material to see what is there, then going on to Chapter 7. Chapter 7 is based upon a series of demos, which can be downloaded from www.smxrtos.com/securesmx, and which are designed to get you going as quickly as possible. You can refer back to the theory chapters when you need more details.

Chapter 8 provides much needed debug help. Appendix A is the API reference for SecureSMX, Appendix B is a complete linker command file, and Appendix C is a glossary of special terms used in this manual.

Although the SecureSMX methodology is not rocket science, it is probably much different than what you are used to. Hence, studying the theory sections, as needed, will avoid misconceptions about how things actually work.

# 1.2 Partitioning

SecureSMX adds strong security and reliability to the SMX RTOS. It is a next generation RTOS that provides tools and methods to improve the security of systems using Micro Controller Units (MCUs) with Memory Protection Units (MPUs). SecureSMX currently supports ARM Cortex-M MCUs. It facilitates dividing embedded software into isolated partitions through the use of the processor's memory protection unit (MPU) and its privilege levels.

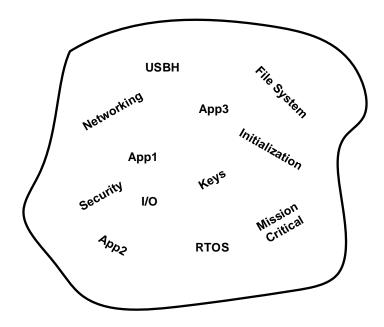

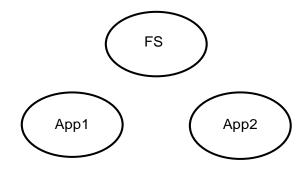

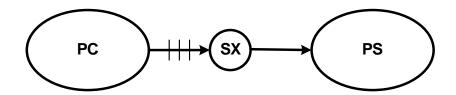

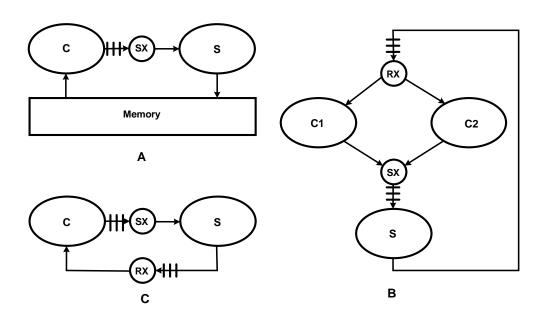

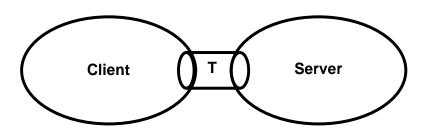

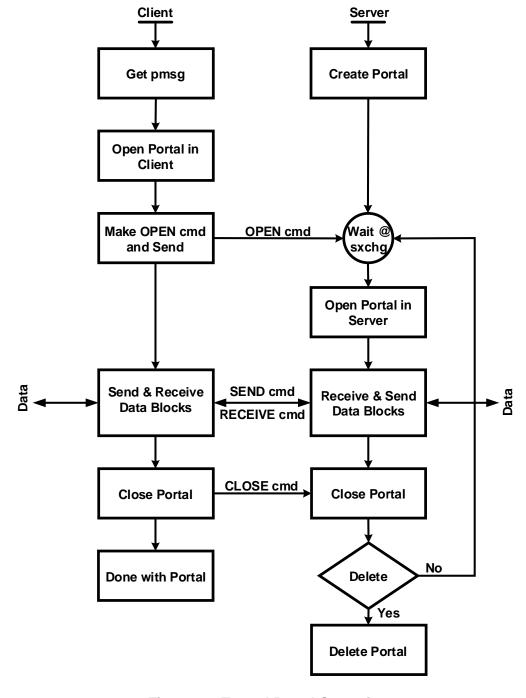

Figure 1.1 shows typical embedded system software. Everything is jumbled together. If a hacker gains access anywhere, he has access everywhere. Likewise, a bug anywhere in the system jeopardizes the whole system.

Figure 1.1 Non-Partitioned Software

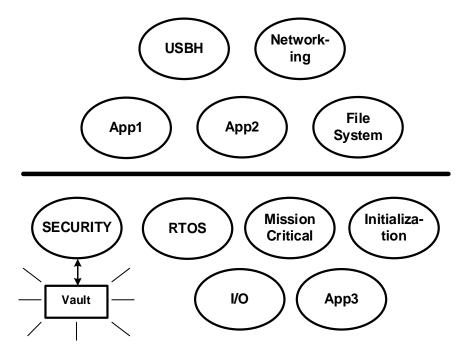

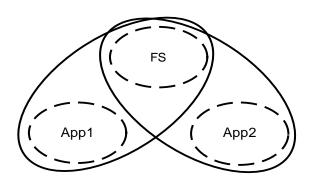

Figure 1.2 shows the same embedded system software after partitioning.

Figure 1.2 Partitioned Software

Because the above partitions are fully isolated from each other, by hardware, if a hacker gains access to one partition, he cannot gain access to other partitions. Hence he can only disable the partition that he has penetrated and he cannot obtain keys and critical information contained in

the Vault and other partitions. Likewise, a bug in one partition can damage only the operation of that partition. In both cases, system monitoring software can be alerted and it can take corrective action as well as notifying the operator or a monitoring center. In the above figure, App3 may be in pmode because it needs direct access to system services or needs maximum performance.

# 1.3 Advantages of Isolated Partitions

Dividing embedded system software into isolated partitions has the following benefits:

- 1. Much better security from hackers.

- 2. Higher reliability and safety.

- 3. Isolation of low-quality or unknown-quality software.

- 4. Better plug-in modularity.

- 5. More disciplined design.

- 6. Immediate detection of null and wild pointers and stack and buffer overflows.

- 7. Easier incorporation of legacy software, due to enforced modularity.

- 8. Partition-only reboot rather than system reboot for recovery.

- 9. Support for partition-only updates.

Security and Reliability are two sides of the same coin. In the former, hacks are deliberate; in the latter, bugs and malfunctions are accidental. However, both damage system operation, and measures that improve one tend to improve the other. Partitions are often subsystems that perform specific functions, e.g. file systems, networking systems, etc. Hardware enforcement of full isolation enforces modular designs and better module reusability in future systems. Hardware enforcement of better design practices is also desirable. Partial reboots and partial updates save time. These are all good reasons for partitioning.

#### 1.4 Hardware

SecureSMX utilizes the following security features of the Cortex-M ARMM7 and ARMM8 architectures:

- 1. Memory Protection Unit (MPU).

- 2. Privileged and Non-privileged processor levels.

- 3. SVC Exception.

The methodology presented in this manual is the same for both processor architectures. Hence it can be applied to families of products that use both architectures and it permits smooth migration from ARMM7 to ARMM8. The only difference is that the ARMM7 MPU is more difficult to support, however SecureSMX provides methods to overcome its problems. SecureSMX does not require ARMM8 TrustZone in order to provide high security and protection from attacks and

software bugs. For ARMM8, it runs in the *non-secure state*, but it could run in the *secure state*, if preferred.

In the code and in this manual, ARMM7 represents ARMv7-M and ARMM8 represents ARMv8-M.

### 1.5 Methodology

As evidenced by the breadth and depth of this manual, SecureSMX presents a comprehensive methodology for the design of high-security embedded systems. This new methodology is quite different from doing things the old way. Be prepared to learn some new tricks. The theoretical aspects of the new SecureSMX methodology are explained in chapters 2 through 6.

Full partition isolation requires the following:

- 1. Limiting code, data, and I/O region access via the MPU.

- 2. Restricting access to system services via the SVC exception.

- 3. Dedicated heap for each partition that requires a heap.

- 4. Portals for communication between partitions.

- 5. Runtime, service, and object access limitations.

Chapters 7 and 8 cover the design and debug techniques necessary to partition embedded system software. Refer to the Glossary for unfamiliar terms.

# 1.6 Security

#### 1.6.1 The Increasing Need for Security

Most embedded systems have little or no security built in, yet they are being connected into the Internet of Things (IoT) at a rapid pace. As a consequence, once isolated, defenseless embedded systems are becoming accessible via the Internet. This makes it much easier for hackers to gain access and to do damage, not only to the devices, but also, through them, to entire systems.

#### 1.6.2 Protection Goals

The **primary goal** of protection is to protect trusted, critical software and data from less-trusted, non-critical software, which has become infected with malware or is buggy. Examples of trusted software are: the RTOS kernel, exception handlers, security software (e.g. crypto, authentication, secure boot, and secure update), and mission-critical software. Examples of less-trusted software are: code vulnerable to malware attacks such as: protocol stacks, device drivers, software of unknown pedigree (SOUP), and insufficiently tested new code.

The **secondary goal** is to detect intrusions and bugs and shut them down so that critical system operation is not imperiled, and sensitive data is not stolen. Dealing with intrusions and bugs may be handled by stopping and restarting a penetrated partition or may require stopping and rebooting the entire system.

The **tertiary goal** is to minimize the amount of trusted code that must be written, since it is more difficult to write trusted code. Code that is less trusted can be run in unprivileged mode (umode) partitions, which are strongly isolated from trusted code partitions. This insures that failures or hacking of less-trusted code will not impair the critical function of the system – e.g. to keep a patient alive or to control a dangerous machine.

The degree of protection that must be implemented depends upon the security and safety requirements of a specific system and the threats to which it may be exposed. SecureSMX provides a range of security tools that enable achieving a level of protection appropriate for a given system. And security can be steadily improved, in future releases, as a system becomes more widely distributed and therefore more likely to be attacked. SecureSMX is structured to foster progressive security improvement.

#### 1.6.3 What You Need

SecureSMX is not a complete security solution. You also need:

- 1. Secure boot.

- 2. Secure update.

- 3. System monitoring.

SMX middleware products do provide crypto and authentication software.

# 1.7 SecureSMX Snapshot

The main things SecureSMX does to achieve better security and reliability in a multitasking system are as follows:

- 1. Allow defining different MPU regions for each task.

- 2. Perform MPU region switching during task switches.

- 3. Automatically generate regions from linker command files.

- 4. Provide a Supervisor Call (SVC) API to allow unprivileged code (ucode) to call system services, as well as to limit which services can be called from ucode<sup>1</sup>.

- 5. Allow allocation of protected blocks and messages.

- 6. Run mission critical code trusted code in privileged mode (pmode) tasks and partitions.

- 7. Run middleware and application code in unprivileged mode (umode) tasks and partitions.

- 8. Run the SMX RTOS kernel APIs, LSRs, ISRs, scheduler, error manager, and other system services in hmode.

<sup>&</sup>lt;sup>1</sup> See Appendix D: SMX API Limitations.

- 9. Provide protection for both ptasks and utasks.

- 10. Individually protect task stacks.

- 11. Provide portals for communication and operations between fully isolated partitions.

- 12. Provide runtime limiting.

- 13. Control system object accesses via tokens.

- 14. Allow tasks to have privilege levels.

- 15. Provide a method to move most ISR code into a umode partition.

SecureSMX has had these principal design goals:

- 1. To enable developers to achieve high security for their systems.

- 2. To support incremental security improvement for existing systems as well as to provide a security base for new systems.

- 3. To provide a flexible solution that permits achieving the right level of security for a given system.

### 1.8 SecureSMX Licensing

SecureSMX is made available under the Apache License, Version 2.0. It is protected by several U.S. patents, which are listed in smx.h, and patents pending. A patent license is granted according to the Apache License for the use of SecureSMX in OEM products but not to remove and integrate code with another OS, RTOS, or kernel. This is only a summary of intent; please see the actual license terms in license.txt and apache2.txt in the release and the comment block at the top of each source file.

Support and contracting services are available from Micro Digital at support@smxrtos.com.

# **Chapter 2 Background**

#### 2.1 MMUs vs. MPUs

Memory Management Units (MMUs) are used with full Operating Systems (OSs), such as Linux and Windows to provide *isolated virtual memories* for *processes*. Processes are independently compiled and linked and then individually loaded and run by the OSs. Process to process isolation is good enough that if a process becomes infected by malware or starts malfunctioning, for any reason, the OS can usually shut it down with little or no damage to other processes nor to the system, itself. Hence, security is good, with regard to infected processes. The use of MMUs is well-studied and well-understood. A downside to using MMUs is that they typically require high-performance processors and very large memories.

High-performance, power-hungry, expensive processors and very large memories are not compatible with the requirements for most embedded systems. In addition, full OSs do not have the response times needed for many real-time applications. Most embedded systems use low-cost, low-power, moderate-performance Micro Controller Units (MCUs) controlled by Real Time Operating Systems (RTOSs). Embedded systems usually have meager memories and processors compared to full OS systems. For security, many MCUs offer Memory Protection Units (MPUs); these are faster than MMUs but not capable of creating virtual address spaces. Instead, they allow dividing memory into isolated regions within a single address space.

In most embedded systems, we deal with *partitions* instead of *processes*. The idea is basically the same – partitions include one or more tasks and perform specific functions for a system. Just like processes, it is desirable to isolate partitions from each other so that if one partition is infected with malware or begins malfunctioning, it can be stopped with minimal damage to the rest of the system. Unfortunately, this is not as easy to accomplish with MPUs as it is with MMUs.

The biggest challenge is that all MCU software is compiled and linked into a single executable that runs in a *single address space*. Also, MPUs impose limitations of their own. The use of MPUs for security is not well-studied, nor well-understood, and there are many complex tradeoffs involved, especially due to the above limitations of embedded systems and the need for deterministic real-time performance.

An advantage of MPUs over MMUs is that switching from one partition or process to another is faster. In MMU systems it may be difficult to meet response time requirements. Such systems are usually referred to as *soft real-time systems* as opposed to *hard real-time systems* implemented with MCUs.

# 2.2 Cortex Micro Controller Units (MCUs)

#### 2.2.1 Cortex-M

The Cortex-M processor architecture, which includes ARMM7 and ARMM8, offers the following security features:

- 1. Privileged and Unprivileged levels of processor operation.

- 2. Supervisor Call (SVC) Instruction.

- 3. Memory Protection Unit (MPU).

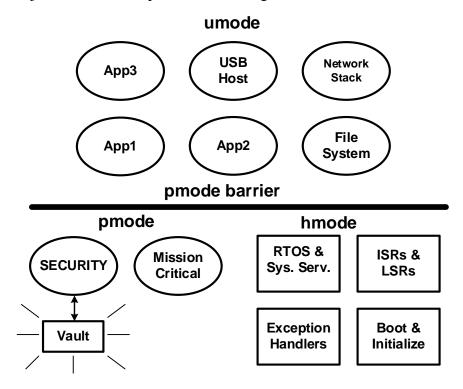

The first is implemented via the three modes of processor operation:

- 1. Handler Mode: Privileged mode for ISRs, fault handlers, the SVC handler, and the PendSV handler. This mode can be entered only via an interrupt or an exception. We refer to handler mode and any non-task, privileged code that uses the main stack as being in *hmode*.

- 2. Privileged Thread Mode: Privileged tasks (ptasks) run in this mode. It can be entered only from handler mode, by setting CONTROL.nPRIV = 0. We refer to this as *pmode*.

- 3. Unprivileged Thread Mode: Unprivileged tasks (utasks) run in this mode. It can be entered from either of the above two modes, by setting CONTROL.nPRIV = 1. We refer this as *umode*.

The p prefix can be interpreted either as *privileged* or *protected* and the u prefix can be interpreted as either *unprivileged* or *user*. Code and tasks that run in pmode are called *pcode* and *ptasks*; code and tasks that run in umode are called *ucode* and *utasks*.

An important aspect of the Cortex-M architecture is that pmode can be entered only via an interrupt or an exception. The SVC N instruction causes an exception. It can be executed from umode with an 8-bit argument, N. This allows making a system call from umode where N specifies the function to call. The called function executes in pmode and returns its result to the umode caller transparently. The SVC N instruction can also execute from pmode, which is helpful for migrating a partition from pmode to umode.

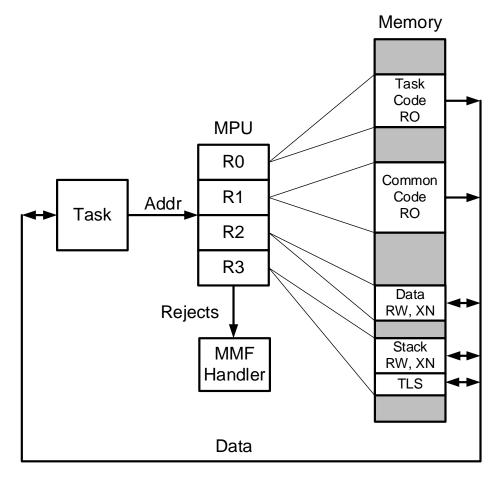

The MPU provides N *slots* for N *regions*. Each region has a starting address, a size, and access parameters, such as Read-Only (RO), Read/Write (RW), eXecute Never (XN), etc. If a memory access is not permitted by a region in the MPU, a Memory Manage Fault (MMF) is generated. The MMF is an exception that causes the MMF Handler to run. It normally stops or deletes the faulting task and initiates recovery.

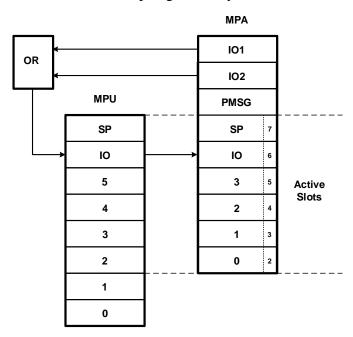

Figure 2.1 MPU Operation

Figure 2.1 shows a simplified MPU with only 4 slots. Most MPUs have 8 slots, some have 16. The region stored in R0 is a Read Only (RO) region for task code. R1 is an RO region for code that is common with other tasks. R2 is a Read/Write (RW) and eXecute Never (XN) region for data. R3 is the task stack, which is also RW and XN. Also shown also is optional Task Local Storage (TLS) that can be part of the task stack region and which can be used for local task data, such as a buffer.

Probably, the biggest drawback of the Cortex-M MPU is insufficient slots. Nearly all Cortex-M processors have 8-slot MPUs. This would seem to be enough, but actually 10 or 12 would be better. SecureSMX provides several methods to deal with this problem

#### 2.2.2 Cortex-M ARMM7

The ARM Cortex-M ARMM7 processor architecture was introduced in 2005 and was intended for medium-size embedded systems. Since then, thousands of different Cortex-M ARMM7 based Micro Controller Units (MCUs) have been developed by the semiconductor industry; they are used in tens of thousands of products developed by device manufacturers; and billions of chips have been shipped to date. It is by far the most dominant MCU architecture (70% market share) and hence the one we have supported first.

A serious limitation of the ARMM7 MPU is that region sizes must be powers-of-two and regions must be aligned on their size boundaries. This tends to result in substantial memory waste, which is probably why this MPU has been very unpopular and seldom used in embedded systems. However, we have found several methods to deal with this problem and to reduce memory waste to acceptable levels, thus opening up this MPU to serious use for security improvement.

Each region is divided into 8 subregions and each subregion can be individually disabled. This permits overlapping the unused portion of one region with another region and is one method used by SecureSMX to reduce memory waste.

#### 2.2.3 Cortex-M ARMM8

The Cortex-M ARMM8 architecture was announced several years ago. It requires that region sizes and alignments only be multiples of 32 bytes. This effectively eliminates the memory waste problem of the ARMM7 architecture. However, the number of MPU slots is unchanged, and a new problem has been introduced: region overlap is not permitted. This is a serious and unnecessary break with the ARMM7 architecture. It creates an obstacle to porting software from one to the other and causes increased complexity, as is discussed in later sections.

The Cortex-M ARMM8 architecture also offers a new feature called *TrustZone*®, which permits secure and non-secure states. TrustZone secure state may good for storage of keys and other private data. However, running code in secure state may not be worth the extra code complexity and debug difficulty. In addition, we believe that most device manufactures will want a security solution that works with both ARMM7 and ARMM8 processors. Therefore SecureSMX does not require nor support TrustZone.

# **Chapter 3 Getting Started**

SecureSMX supports both upgrading legacy code security and providing a secure foundation for new code. We start with legacy code.

### 3.1 Legacy Code